## Recent Trends and Challenges onLow Power FinFET Devices

M. Chandra Sekhar Reddy<sup>1</sup>, N. Yerriswami<sup>2</sup>, J. Hema Madhuri<sup>3</sup>

<sup>1</sup>Professor, <sup>2</sup>Assistant Professor, <sup>3</sup>Assistant Professor, ECE Department, Anantha Lakshmi Institute of Technology and Sciences, Ananthapuramu, Andhra Pradesh, India.

**Abstract**: Due to the rapid growth on electronic industries, the revolution on Integrated circuits still plays a major role. Over the last few years, research works on Integrated circuits is going on scale down the devices dimensions in order to attain small size as well as improvement in speed of circuits. Regardless of the progress in the area of VLSI design Bulk CMOS technology which consumes very less power. But one of the most important breakthroughs of this technology is short channeling property. In advanced digital application the key constraint is low off state leakage current, while we scale the device dimension. And it must maintain high driving capability. Here FinFET overcomes short channel effects as well as it exhibits high driving current capability even in nano scale channel. Recent developments in FinFET's have increased the need for off state leakage current along with high speed switching devices.

-In the past decade, a number of studies have sought to determine different FinFET based devices. Previous studies in this area of research have reported the types of FinFET's along with different applications. This paper presents a literature review on FinFET based different devices. And a bird eye review for advanced FinFET's is presented in this literature work. This literature work reviews on some research papers.

**Keywords:** Bulk CMOS devices, FinFET devices, short channel effects, off state leakage current power consumption.

### **1** Introduction

Over the past three decades, electronics revolution in an IC is scale down the devices dimensions from 320nm to 45nm. This scale down process is building blocks of CMOS technology. As the IC technology changes form micron devices to submicron devices, it has major factors like achieving low cost & high performance devices are the challenges for the production. But CMOS have its own constraints.

Many researchers will identify the drawbacks in cmos technology while we scale down the device dimension. Among those we have basic drawback of short channel effects will raise to bulk CMOS device OFF state transition leakage current. That bulk cmos devices doesn't meet the specifications of the industries, because of its lower transistor drive current. And gate oxide thickness is also an important issue while considering scaling factor. We have basic limitation for gate oxide thickness, when it crosses its limitation will cause an unexpected gate leakage current.

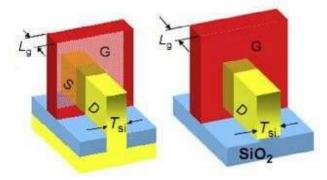

After this researchers will overcome those problems by making high permittivity gate dielectrics i.e. (High-K) [1]. When we maintain low sheet resistance will causes high driving current. Due to this reason technology gradually changes form bulk silicon CMOS devices to Ultra thin body transistors. This ultra thin body transistors leads to reduce sub surface leakage paths by making thin silicon on insulation process. But a thin body mos transistor consists of very high parasitic drain and source resistance. Figures of bulk type si mos transistor and ultra thin mos transistors are shown in below fig 1a and 1b. Ultra thin body mos transistors have least effective controlled gate.

Fig 1.a Bulk mos transistor

Fig 1.b Ultra thin mos device

### Dogo Rangsang Research Journal ISSN : 2347-7180

### UGC Care Group I Journal Vol-11, Issue-11, No. 02, November 2022

For attaining high driving current through ultra thin body devices we have to maintain bottom silicon substrate body as thinner as we can. And thicker source and drain terminals will leads to minimizing the parasitic resistance. Hence these systems will drive high driving current. A new low pressure chemical vapor deposition process is included for thicker source and drain terminals. By increasing the threshold voltage of pmos transistor and nmos transistor of ultra thin body leads to decreases the thickness of the body. This body thickness has an impact on sub-band spacing. They both are inversely proportional to each other. This will leads to a decreasing the effective mass and increases the mobility factor. But the major challenges in ultra thin mos devices are having high series resistance of the thin body. This will overcomes by the FinFET devices.

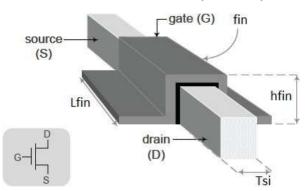

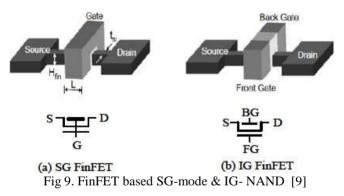

In cmos we have lot of short channel effects with threshold voltage variations will overcomes by using the multi gate devices [1]. Multi gate devices are non planar devices. Which have in different modes like short gated mode, independent gated mode, and low power mode. Among those we considered short gated mode type multi gate transistors. These transistors have two gates which one gate is shorted to another gate for additional controlling to the gate terminal. Basic non planar FinFET devices shows in fig.2

Figure.2 non-planar FinFET devices [2]

In this paper we present logic gates based realization of FinFET's. Basically we focused on Universal gates along with Xor and Xnor FinFET Design, through predictive technology model (PTM).

### 2 Trends in FinFET Logic Design

The literature on FinFET based Logic circuits shows a variety of approaches. Here we focused on most research papers regarding to FinFET devices. And also we verified those by using predictive technology and BSIM-CMG models. Circuit design parameters like Fin width, Fin height and Fin Pitch along with gate parameters are verified by using multigate MOSFET technology Springer article [2]

### A. Massimo Alioto "Analysis and Evaluation of Layout Density of FinFET Logic Gates" 2009 IEEE International Conference on Microelectronics [3]

In this paper author compared layout density between bulk CMOS logic gates and FinFET logic gates. Author considered FinFET 3T/4T logic gates .

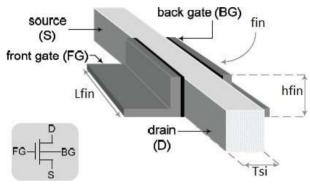

Figure 3(a). 3T FinFET physical structure [3]

Here author also mentioned the Area occupancy compared to the CMOS 65nm standard type to FinFET multigate transistor. This result shows that area overhead problem of planar CMOS bulky transistors overcomes by using n channel stacking process of FinFET devices.

Figure 3(b). 3T FinFET physical structure [3]

# **B.** Ravindra Singh Kushwah, Manorama Chauhan "Modeling and simulation of FinFET circuits with Predictive technology models", 2014 [4]

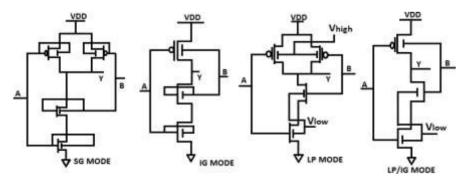

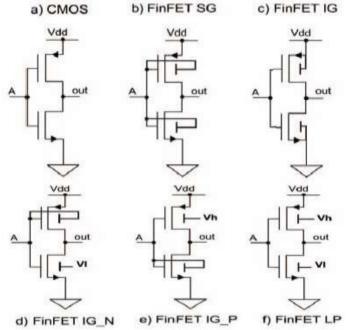

In this paper authors mentioned that basic four types of FinFET models i.e. SG mode (shorted gated mode), IG mode (independent gated mode), low power mode and hybrid IG-mode with LP mode (low power). Author consider one nand gate logic design through all FinFET models.

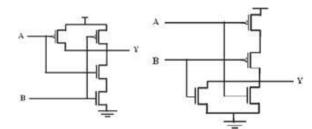

Figure 4. FinFET based NAND & NOR [4]

For simulation they are used BSIM-CMG 45nm technology with cadence virtuoso simulation tool. Author compared all the nand gate based models. Among those short gated model and independent gate model have high noise tolerance compared to low power gate and low powered independent gate model. And short gated mode and independent gate model have 40% of low leakage power, 25% of low power consumption and 20% of low tolerance compared to low power gated and low power independent gated model. Coming to the delay it is 10% of low power model and low power independent model compared to short gated model and independent

### UGC Care Group I Journal Vol-11, Issue-11, No. 02, November 2022

gated model[4]. And finally the speed, low power model has higher speed than the other models. Finally short gated model of FinFET nand gate design 35 to 45% of low leakage power than the other model FinFET nand gates. Independent gate and low power independent gate devices required very less no. of transistors means it occupies very less area compared to other models. But it has a design limitation like fin height and fin width.

C. Sapana S. Nalamwar, Prof. Smita A. Bhosale "Design of low power logic gates by using 32nm and 16nm FinFET technology" 2015 [5]

In this paper author verified that FinFET based nand and nor gates. Simulation is going through by using predictive technology model files of 32nm cmos and 32nm FinFET. Authors differentiate the factors of static power, dynamic power and current flowing through the cmos and FinFET systems using 32nm model and 16nm model.

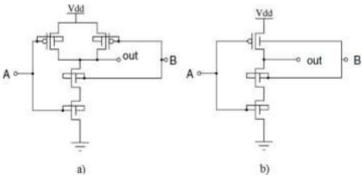

Figure 5. FinFET based nand & nor [5]

And they applied According to the results 0.8v is the minimum to operate the cmos and FinFET device at 32nm model. And for 16nm model cmos doesn't operates. But in case of FinFET it will operates at 0.3v. The dynamic power issue in FinFET nand gate it is 436.61 nW, for nor gate it is 439.99 nW in 32nm model [5]. Where in 16nm model it is reduced to 187.30nW for nand and 200nW for nor gate. Hence author said that when we decreasing the channel length of the device in FinFET then it will greatly reduces dynamic and static power of the device. And also compared to nor gate based FinFET, nand gate based FinFET device have better static and dynamic power consumption.

### D. Cristina Meinhardt and Ricardo Reis "FinFET Basic Cells Evaluation for Regular Layouts", 2013 IEEE [7]

In this paper author designed independent gate based FinFET Nand gate design and observed it significantly improved delay and power factors of the previous cases. Independent gate FinFETs achieved area reduction up to 20% compared to the other low power FinFET gate models [7].

Fig 8. FinFET based SG-mode NAND & NAND [7]

Author compared all three designing models of FinFET and observed power, timing and area constraints of the nand gate design. Independent gate FinFET are similar to CMOS bulky transistor but the operation of transistor is slower than the Short gated FinFET devices. In power parameter independent gate FinFET mode consumes very less power. but it has its own limitations.

E. Cristina Meinhardt, Ricardo Reis "Comparing High-Performance Cells in CMOS Bulk and FinFET Technologies", 2014 IEEE [8]

### UGC Care Group I Journal Vol-11, Issue-11, No. 02, November 2022

But in this paper author verified 32nm technology library.and results are compared with static and dynamic power dissipation of the device.

Fig 8.CMOS & FinFET SG, IG, and LP mode [8]

By using the predictive technology model PTM of FinFET gives you better delay result compared to TCAD simulation tool. But it has extensively increasing the design rules based layout design [8]. Regular layouts may have an effect of routing problems

#### F. Xuqiang Zhang, Jianping Hu, Xiaoyan Luo "Optimization of Dual-Threshold Independent-Gate FinFETs for Compact Low Power Logic Circuits", 2016 IEEE [9]

In this paper author designed independent gate FinFET design compared to short gated FinFET model.

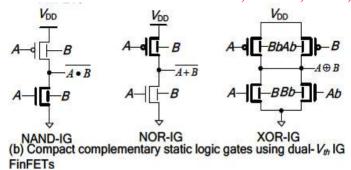

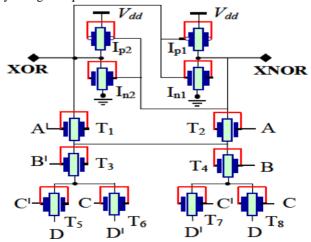

Author designed independent gate mode and short gated mode FinFET NAND and NOR circuits along with differential cascade voltage switching logic based xor and xnor circuits.

**Dogo Rangsang Research Journal UGC Care Group I Journal** Vol-11, Issue-11, No. 02, November 2022 ISSN : 2347-7180 ⊣]+ ⊣[⊦ -]}--4[- -]}--4[-∄⊢⊸н∃ SG High-Vth IG Low-Vth SG Low-Vth IG High - Vth  $V_{DD}$  $V_{DD}$  $V_{DD}$ Ab of **⊢∣⊶**₿ ᠳ⊟ R  $A \bullet B$ -A⊕B A + BH-Ab R ٦L -**B**b R NAND-SG NOR-SG XOR-SG (a) Complementary static logic gates using SG FinFETs

The result of short gated mode is compared with dual threshold independent gate FinFET mode device. By using dual threshold IG mode FinFET based static and DCVSL[9] will get low power delay compared with Short Gated FinFET's.

# G. Neha Yadav, Saurabh Khandelwal, Shyam Akashe "Design and Analysis of FINFET Pass Transistor Based XOR and XNOR Circuits at 45 nm Technology", 2013 [10]

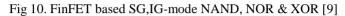

In this paper author designed xor and xnor system based on FinFET pass transistors logic. And also along with this they considered short gated model for designing xor and xnor systems.

Fig 12. FinFET based IG-mode XOR-XNOR mode [10]

Author verified product of power delay and energy delay for xor and xnor FinFET devices consumes very less power and high speed systems compared to other models in FinFET's. But it has certain limitations to design below 45nm[10].

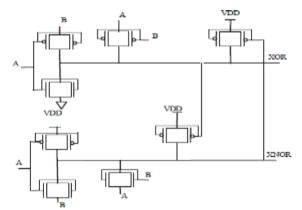

### H. Sarada Musala, Student Member, IEEE, Avireni Srinivasulu, Senior Member, IEEE "FinFET Based 4-BIT Input XOR/XNOR Logic Circuit", 2016 IEEE [11]

In this paper Author designed 4 bit XOR/XNOR circuit using pass transistor FinFET logic. With a full voltage swing at the output will produces good driving capability at high frequencies also.

UGC Care Group I Journal Vol-11, Issue-11, No. 02, November 2022 Fig 13. FinFET based XOR-XNOR [11] The structure is simple to design. This pass transistor based FinFET design has very less delay because of its critical path consists of less number of transistors. And also author verified power consumption is also better than previous case.

### **3** Challenges in FinFET based Design

An advanced FinFET device has multi-gate short circuit gate mode and independent gate mode 3D transistor. While compared to CMOS bulky planar transistors, FinFET has efficient improvement in power consumption and performance. And also it has better electrical property along with great reduction in dynamic power as well as static (leakage) power.

For an advanced FinFET technology i.e. 10nm technology, it has some major design challenges. These are in analog, digital, parasitic and signoff perspectives..

- While fabricating the FinFET device we need an additional masking for correct printing at below 20nm design technology

- For layout designing at 28nm or below becomes more complicated with additional nodes requirement.

- For the metal layers resistivity it consists of 50 Times or more potentials are required

- For all the low process node operation Electro-migration will dramatically increases

- More number of complicated fabrication based design rules

- As we design millions of gates in fabrication gives an more time to market

But it had an advantage for Designers can improved performance by working at lower voltages.

### 4 Conclusion

In this paper presents a review on FinFET based logic gates. FinFET devices are advanced devices which greatly reduces our short channel effects in cmos devices. As well as when we scale down the channel length of the device static and dynamic power is also reduced. We considered design parameters of FinFET devices and also how those FinFET parameters are modeled by using Predictive technology model. Various FinFET models also discussed in this review papers.

### References

- [1] P Mishra, <u>A Muttreja</u>, <u>NK Jha</u> Nanoelectronic Circuit Design, 2011 Springer, pp: 23-55

- [2] Mutigate MOSFET technology, Weize (Wade) Xiong "FinFETs and Other Multi-Gate Transistors", Jean-Pierre Colinge (Ed.) ISBN 978-0-387-71751-7

- [3] Massimo Alioto "Analysis and Evaluation of Layout Density of FinFET Logic Gates" 2009 IEEE International Conference on Microelectronics.

- [4]Ravindra Singh Kushwah, Manorama Chauhan, Pavan Shrivastava, and Shyam Akashe "Modeling and simulation of FinFET circuits with Predictive technology models" *Radioelectronics and Communications Systems*, 2014, Vol. 57, No. 12, pp. 553–558.

- [5] Sapana S. Nalamwar, Prof. Smita A. Bhosale "Design of low power logic gates by using 32nm and 16nm FinFET technology" International Conference on Energy Systems and Applications (ICESA 2015).

- [6] Anish Muttreja, Niket Agarwal and Niraj K. Jha "CMOS Logic Design with Independentgate FinFETs",2007 IEEE International journal.

- [7] Cristina Meinhardt and Ricardo Reis "FinFET Basic Cells Evaluation for Regular Layouts", 2013 IEEE international journal.

- [8] Cristina Meinhardt, Ricardo Reis "Comparing High-Performance Cells in CMOS Bulk and FinFET Technologies",2014 IEEE International journal.

- [9] Xuqiang Zhang, Jianping Hu, Xiaoyan Luo "Optimization of Dual-Threshold Independent-Gate FinFETs for Compact Low Power Logic Circuits", 2016 IEEE international conference.

- [10] Neha Yadav, Saurabh Khandelwal, Shyam Akashe "Design and Analysis of FINFET Pass Transistor Based XOR and XNOR Circuits at 45 nm Technology", 2013 International Conference on Control, Computing, Communication and Materials (ICCCCM).

- [11] Sarada Musala, Student Member, IEEE, Avireni Srinivasulu, Senior Member, IEEE "FinFET Based 4-BIT Input XOR/XNOR Logic Circuit", 2016 IEEE international journal.

- [12] S.A. Tawfik, V. Kursun. FinFET technology development guidelines for higher performance, lower power, and stronger resilience to parameter variations. 52nd IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), 2009, pp.431-434.

- [13] D. D. Lu, A.M. Niknejad, C. Hu, C.-H. Lin, Compact modeling of variation in FinFET SRAM cells, IEEE Design & Test of Computers, pp. 43-50, March/April 2010.

- [14] J. Hu, Y. Zhang, C. Han, and W. Zhang, "An Investigation of Super-Threshold FinFET Logic Circuits Operating on Medium Strong Inversion Regions," The Open Electrical & Electronic Engineering Journal, vol. 9, no. 1, 2015.

- [15] M. Rostami, K. Mohanram, Dual-Vth independent-gate FinFETs for low power logic circuits, IEEE Tran. on CAD of Integrated Circuits and Systems, Vol. 30 (3), pp. 337-349, March 2011.

- [16] S. A. Tawfik and V. Kursun, Multi-threshold voltage FinFET sequential circuits, IEEE Trans. on Very Large Scale Integration (VLSI) Systems, Vol. 19(1), pp. 151-156, Jan. 2011.

- [17] M. C. Wang, "Independent-gate FinFET circuit design methodology," IAENG International Journal of Computer Science, vol. 37, no. 1, 2010.

- [18] N.Paydavosi, S. Venugopalan, Y. S. Chauhan, J. P. Duarte, S. Jandhyala, A.M. Niknejad, C. C. Hu, BSIM - SPICE models enable FinFET and UTB IC, IEEE Acess, Vol. 1, pp. 201-215, May 2013.

- [19] M. Masahara, Y. Liu, K. Sakamoto, K. Endo, T. Matsukawa, K. Ishii, T. Sekigawa, H. Yamauchi, H. Tanoue, S. Kanemaru, H. Koike, E. Suzuki, Demonstration, Analysis, and Device Design Considerations for Independent DG MOSFETs, IEEE Transactions on Electron Devices, Vol. 25 (9) pp. 2046 2053, 2005.

- [20] B. Zahiri. Structured ASICs: Opportunities and Challenges. In: 21st ICCD, pp. 404- 409, 2003.

- [21] C. Meinhardt; R. Reis. FinFET basic cells evaluation for regular layouts, IEEE 4th Latin American Symposium on Circuits and Systems (LASCAS), 2013.

- [22] ITRS <u>www.itrs.net/Links/2011ITRS/2011Chapters/2011ExecSum</u>. df

- [23] E. J. Frank et al. "Device scaling limits of Si MOSFETs and their application dependencies". Proc.IEEE, 89(3):259–288, Mar. 2001.

- [24] T.-J. King. "FinFETs for nanoscale CMOS digital integrated circuits". In Proc. Int. Conf. Computer-Aided Design, pages 207–210, Nov. 2005.

- [25] Narendar, V. et al. Design of High-performance Digital Logic Circuits based on FinFET Technology. Int. Journal of Computer Applications, v.41, n.20, march, 2012.

- [26] S. Sinha, G. Yeric, V. Chandra, B. Cline, Y. Cao, Exploring sub-20nm FinFET design with predictive technology models, DAC, 2012.

- [27] Weimin Zhang, J.G. Fossum, L. Mathew, Yang Du: Physical insights regarding design and performance of independent-gate FinFETs. IEEE Transactions on Electron Devices 52-10, 2198 (2005)

- [28] S. Eminente, Kyoung-Il Na, S. Cristoloveanu, L. Mathew, A. Vandooren: Lateral and vertical coupling effects in MIGFETs. Proceedings of the IEEE International SOI Conference, 94 (2005)

- [29] K. Endo, Y. Liu, M. Masahara, T. Matsukawa, S. O'uchi, E. Suzuki: Fabrication and power-management demonstration of four-terminal FinFEts. ECS Transactions 6-4, 71 (2007)

- [30] J.P. Colinge: Fully-depleted SOI CMOS for analog applications. IEEE Transactions on Electron Devices 45-5, 1010 (1998)

- [31] L. Mathew, Y. Du, A.V.Y. Thean, M. Sadd, A. Vandooren, C. Parker, T. Stephens, R. Mora, R. Rai, M. Zavala, D. Sing, S. Kalpat, J. Hughes, R. Shimer, S. Jallepalli, G. Workman, W. Zhang, J.G. Fossum, B.E. White, B.Y. Nguyen, J. Mogab: CMOS Vertical Multiple Independent Gate Field Effect Transistor (MIGFET). Proceedings IEEE International SOI Conference, 187 (2004)

- [32] M.C. Lemme, T. Mollenhauer, W. Henschel, T. Wahlbrink, M. Baus, O. Winkler, R. Granzner, F. Schwierz, B. Spangenberg and H. Kurz: Subthreshold behavior of triple-gate MOSFETs on SOI Material. Solid State Electronics 48-4, 529 (2004)

- [33] X. Baie, J.P. Colinge, V. Bayot, E. Grivei: Quantum-wire effects in thin and narrow SOI MOSFETs. Proceedings IEEE International SOI Conference, 66 (1995)

- [34] J.P. Colinge, X. Baie, V. Bayot, E. Grivei: A silicon-on-insulator quantum wire. Solid-State Electronics 39, 49 (1996)

- [35] R. Chau, B. Doyle, J. Kavalieros, D. Barlage, A. Murthy, M. Doczy, R. Arghavani, S. Datta: Advanced depleted-substrate transistors: single-gate, double-gate and tri-gate.