# Dogo Rangsang Research JournalUGC Care Group I JournalISSN : 2347-7180Vol-12 Issue-08 No. 07 August 2022HIGH PERFORMANCE OF HAMMING CODE FOR ENCODING AND DECODING WITH<br/>EDA TOOL.EDA TOOL.

Arthi sharma PG Scholar, Department of Electronics and Communication Engineering, CMR Institute of Technology, Hyderabad, Telangana, (Affiliated to JNTU Hyderabad and Accredited by NBA New Delhi)

**Dr.Pradeep Kumar** Associate Professor, Department of Electronics and Communication Engineering, CMR Institute of Technology, Hyderabad, Telangana, (Affiliated to JNTU Hyderabad and Accredited by NBA New Delhi)

## Abstract

In the present day, undeniable level correspondence, and data hypothesis, mess up disclosure and change have uncommon reasonable significance in remaining mindful of data validity across uncontrollable stations. Mess upcoding is extraordinary as a technique for recognizing and refreshing these blunders to guarantee that the data is moved pristine from its source to its objective. Hamming code data touch and equity check are tended to as 4 pieces added of codeword length of 8 pieces, are done. Hamming code (8,4) will be executed at transmitter through glancing through generator system and data input is copied by the result is sent 8 pieces. Something contrary to codeword sent giving 4 pieces yield copied with the considering and recognizing botch conveyed and helping only 1 cycle of a goof by finding its place record 8 pieces inside it at hamming unwinding that equity check structure added. If the hamming result of, the pieces imparted without bungle and with a misstep are copied is "000". manual goof input going about as channel uproar versus got and unravel the right data sent is checked out. Manual mix-up without a doubt and customary circumstances when disturbance changes 1 cycle in correspondence. Botch in more than 1 digit isn't relevant since the structure is only sensible only for Bit Error Rate that is guarantee channel upheaval doesn't change more than 1 cycle. It is known as an Extended Hamming code since the fourth added balance bit is to check twofold missteps or more happened widened Hamming code should be "0". While bungle adjusting procedures see and address the information there is no screw-up. One of the notable methods considering sending mess-up adjustments is Hamming Code. This paper rotates around the ZYNQ-7000 SoC in the game plan and its equipment execution. The course of action coordinates both the encoder and decoder frameworks utilized as successive information transmission and get-together of the far away handset structures. The game plan has been attested utilizing the Vivado2019 test structure. Xilinx zynq-7000 SoC zc702 evaluation unit for Xilinx 19.1 has been utilized for the execution and CADENCE Keywords: Mistake coding, Hamming encoder, and decoder, LFSR, VHDL, ZYNQ7000 SoC, Xilinx

zynq-7000 SoC zc702 assessment pack.

## Introduction

In virtual dispatch structures, normal deterrents and genuine disfigurements can point of view sporadic digit bungles commonly through information transmission. Bungle coding is a strategy for perceiving and overhauling those mistakes in a huge grouping of dispatch structures in PC memory, alluring and optical information garage media and significant district correspondences, satellite, neighborhood, PDA associations, and very nearly other conditions of a virtual information report. Electronic information is imparted over a channel and there may be routinely racketed inside the channel. The uproar can in like manner additionally mangle the messages to be sent. In this manner, the beneficiary gets presumably won't resemble what the source sends. Botch coding has the Goal to update the trustworthiness of virtual dispatch through messes up acknowledgment and blunders correction.

## Error

Information this is communicated over a discussion channel isn't in any way a free slip-up. The insights expelled are provoked due to outside impedance, sign bending, constriction, or clamor. Two

# UGC Care Group I Journal Vol-12 Issue-08 No. 07 August 2022

slip-ups', types. In first is, a slip-up, the handiest the slightest bit is changed and the second, is the burst botches wherein numerous pieces is changed. The various mistakes detection and rectification systems comprising of Cyclic Redundancy Checks (CRC), Parity check, and Hamming Code. This painting makes a specialty of Hamming code.

## Hamming Code

A, for the most part, acknowledged direct Block Code is the Hamming code. the disclosure and correction of a single piece goof in a block of data are done by hamming code. In codes, each piece is associated with an outstanding plan of fairness bits. The region and presence of a single fairness bitbumble are not completely permanently established by separating equities of blends of gotten pieces to make correspondences of all of which a particular piece botch mix of the gotten piece. This is known as the mix-up jumble.

If all get-togethers are right according to this model, it might be contemplated that there is unquestionably not a single piece botch thereof the psyche (there may be different piece botches). In case there are botches in the equities achieved by a lone piece bungle, Erroneous data pieces can be found by including the spots of the social occasions. The easy to execute and are used in Hamming codes are all around used in figuring, telecom, and various applications including data strain and super codes. They are moreover used in negligible cost and low-power applications.

# ZYNQ-7000 SoC

Zynq-7000 SoC First Generation Architecture for most outrageous arrangement flexibility and execution per-watt is overhauled. Twofold focus ARM Cortex-A9 processors are 7 series programmable reasoning consolidated to engage incredibly isolated plans for a wide extent of embedded applications. The Zynq-7000S SoC is the cost better entry feature of the Zynq-7000 SoCs with a singular place ARM Cortex-A9 processor mated with 28nm Artix-7 based programmable reasoning. Zynq-7000 SoC unique design most outrageous arrangement versatility is improved for execution as per watt.

Twofold focus ARM Cortex-A9 processors are 7 series programmable reasoning integrated to engage especially isolated plans for a wide extent of embedded applications. The Zynq-7000S SoC is the cost improved segment feature of the Zynq-7000 SoCs with a lone focus ARM Cortex-A9 processor mated with 28nm Artix-7 based programmable reasoning.

This has integrated programmable reasoning that is related to taking care of a system with more than 3,000 interconnects, past that of a multi-chip plan. The Zynq-7000 SoCs give 10 particular twofold focus contraptions or single-focus to peruse, allowing a flexible stage. for an Innovative ARM® + FPGA designing for partition, assessment, and control. Gas pedals, Extensive OS, middleware, stacks, and IP natural framework.

The various levels of gear and programming security. The coordination is versatile and conveys the genuine programmable stage. System-level execution designing is upgraded and moves low structure power. The most versatile stage for most noteworthy reuse and best TTM Industry-driving. Arrangement devices, Open CL arrangement reflections, and C/C++.

The gigantic course of action of HW& SW design mechanical assemblies, SOMs, plan packs, and reference plans. This is used as Machine Vision Small Cell Baseband, Professional Cameras Programmable Logic Controller, ADAS, and Medical Endoscope.

## Dogo Rangsang Research Journal ISSN : 2347-7180 Xilinx zynq-7000 soc zc702 evaluation kit

Fig 1. Xilinx zynq-7000 SoC zc702 assessment pack.

The Zynq-7000 SoC ZC702 Evaluation Kit incorporates every one of the essential parts of equipment IP configuration devices and pre-checked reference plans including a designated plan, empowering a total implanted handling stage. This empowers a total inserted handling stage including every one of the essential parts of equipment configuration devices IP and pre-checked reference plans with a designated plan by the Xilinx Zynq-7000 SoC ZC702 Evaluation instrument. Two low pin count FMC connectors are appended to VITA-57 FPGA mezzanine cards permitting scaling and customization with little girl cards different highlights can be upheld. The ZC702 board is populated with the Zynq-7000 XC7Z020 SoC which has an SoC-style coordinated handling framework and programmable rationale on a solitary pass on.

# FEATURES

- > Implanted applications utilizing Zynq-7000 SoCs are Optimized for rapidly prototyping.

- > Equipment configuration devices, pre-checked reference plans, and IP.

- > Focusing on the video pipeline is shown as an implanted plan.

- > 1GB DDR3 Component Memory is communicated with Advanced memory.

- ▶ USB OTG, UART, IIC, and CAN Bus is empowering sequential network.

- > implanted handling with Dual ARM Cortex-A9 center processors is upheld.

- Create organizing applications with 10-100-1000 Mbps Ethernet.

- > HDMI out help in Implementing video show applications.

- > The FPGA Mezzanine Card communicates with Expand I/O.

# **DESIGN FLOW for ZYNQ-7000 SoC**

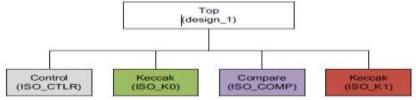

The 7 series and Zynq-7000 IDF rules are illustrated in Isolation Design Flow for Xilinx 7 Series FPGAs or Zynq-7000 SoCs (Vivado Tools). However, the principles for IDF don't contrast among ISE and Vivado, the procedure for execution utilizing Vivado instruments varies. This lab gives subtleties on how capacities are to be disengaged, explicit contrasts between an ordinary segment stream and an IDF parcel stream, and data on IDF-explicit equipment portrayal. Language (HDL). Code memory helpers, and trusted steering rules. To represent the IDF and its capacities, this plan carries out secluded, repetitive Keccak hash modules with a look at the block. It Is a progressive graph of the different VHDL. Sub-blocks were utilized in the execution of this plan.

Fig 2. Plan Hierarchy Block Diagram

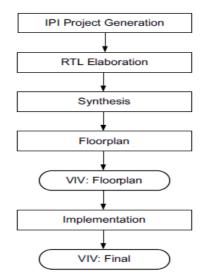

## Fig 3. Vivado IDF Lab Flow Using IP Integrator as the Primary Source Generator

The floorplan for the lab configuration is carried out in an xc7z020clg484-1 gadget that comprises four region gatherings. The first is a region bunch that contains the PS7 site and extra space to course depending on the situation, for example, Advanced extensible Interface signals. The ordinary repetitive framework other three address with analyze module whose clocks and resets come from the processor. While placing the PS7 in a space bunch, make a wall on the full right half of the PS7 block including the primary CLB tile on the lower right corner under the PS7 block see Isolation Design Flow for Xilinx 7 Series FPGAs or Zynq-7000 AP SoCs PS Signals from the PS7 can get to the FPGA texture on the right half of the PS7 site at the extremely least. In the space bunch underneath the PS7, If you really want to impart, you really want to have included a portion of the texture on the right and base to permit correspondence to and from the PS7.

Fig 4. Die View: IDF Lab Floorplan in an xc7z020clg484-1 Device Implementation of Hamming Code on ZYNQ SoC

#### Hamming Code with Matrix Format

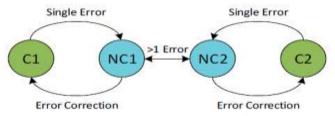

It is the most broadly involved blunder rectifying code application in hamming codes for oneventure translating. They are especially pleasant because of their suitable disentangling idleness and low overt repetitiveness. An (n, k) paired Hamming code, with k information bits and a complete size of n bits, is significant in a straight block code in a n-layered vector space with a k-layered subspace. Here, the codeword is n pieces of the all-out size, of which k is the number of information pieces and p = (n - k) is the number of equality bits. That implies the amount of any two codewords is another codeword implies it is a direct code. A Hamming code is a vital condition for single mistake revision, This implies when there is a solitary blunder in the codeword that has a base distance of 3 that any codeword C1 can change to non-codeword NC1. NC2 however isn't by any stretch inconsistent with non-codeword NC1 through a solitary mistake to some other codeword C2 can change as well. Hence,

# UGC Care Group I Journal Vol-12 Issue-08 No. 07 August 2022

it can without much of a stretch be decoded that the genuine codeword put away was C1that at whatever point the non-codeword NC1 is gotten, An outline of this distance approach. In the mistake, the code needs to have a base distance of (2t + 1) to correct general.

$e = (0\ 0\ 1\ 0\ 0\ 0\ 0)$

$$S = H \times y^T = H \times (c + e)^T = H \times e^T$$

# **Orthogonal Latin Square Codes**

OLS codes depend upon Latin squares and use a bigger part vote for their unwinding system, the Latin square of size m is an  $m \times m$  square lattice with the ultimate objective that the lines and segments, and each number simply appears once in every section or portion of the structure are a difference in the numbers 0 to (m - 1). when superimposed on each other, they produce an original organized set of parts in the new superimposed cross-section into 2 Latin squares that are balanced. The crucial norm of a mix-up correcting OLS code is that there are (2t + 1) independent focal points for re-fostering each data bit. The (2t + 1) equity takes a gander at conditions and free sources including the data bit itself. By and large, in one of the fairness check conditions, different data bits participating in the equity check conditions are phenomenal as in any data bit that occurs. for many missteps  $\leq$  t, at-most t sources are subverted. The uncorrupted sources from botches remain (t + 1). A bigger piece of reasoning translating simply picks the matched worth which occurs in the best number of its pieces of criticism. The (2t + 1) free sources with botches yield the right data ate a result, the larger part vote. OLS codes have k = m2 data bits, where m is the size of the even Latin square. The amount of check pieces is 2tm, where it is the most outrageous number of missteps that the code can address. O LS codes are estimated in the arrangement, and that plans that to address additional bungles, adding 2m check bits for each slip-up is sufficient. For simply 2m equity pieces are normal for a single screw-up correcting code. The SEC code k=1 the correspondence investigates grid a model. In this way, in the larger part balloter picks among 3 free sources (one is the data contact and two more from equity conditions), for the most part, one of which can be changed. Another unraveling approach incorporates calculating the condition and taking the AND of the two problem conditions, any data bit is significant for this case.

This impacts the two its problem conditions, and subsequently, the aftereffect of the AND entrance is 1 is since, assuming that a data bit is in botch. Thusly achieving a 0, can everything thought about degenerate one of the consequences of the AND entrance if a data bit isn't in goof, The AND entryway yield is then XORed with the data spot to make the overhauled outcome.

$$\mathbf{H} = \begin{pmatrix} d_0 & d_1 & d_2 & d_3 & p_0 & p_1 & p_2 & p_3 \\ 1 & 1 & 0 & 0 & 1 & 0 & 0 & 0 \\ 0 & 0 & 1 & 1 & 0 & 1 & 0 & 0 \\ 1 & 0 & 1 & 0 & 0 & 0 & 1 & 0 \\ 0 & 1 & 0 & 1 & 0 & 0 & 0 & 1 \end{pmatrix}$$

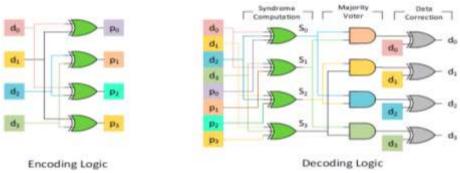

## Fig 6. Equality looks at the framework of an (8, 4) symmetrical Latin square code

Ι

The estimation of equity bits of encoding procedure incorporates. This is the XOR movement of the overall huge number of data bits wherein the uniformity bit is 1 which is 1 in the line of the balance check the lattice out. The system of deciphering incorporates the bigger part vote between the 2t equity check conditions and the data bit itself is worked from the sections of the equity check the network out. In this manner, the decoder for data bit di will have correspondence check conditions from each line of the fairness check grid for which the part di is a 1. The ease of the decoder circuit

# UGC Care Group I Journal Vol-12 Issue-08 No. 07 August 2022

makes it very important for memories with sporadic gets to the essential advantage of the OLS codes. The vast majority of the reasoning translating circuit has outstandingly low torpidity thusly enabling faster understood exercises and accelerating. The encoding circuit and substitute decoder reasoning for each piece in the uniformity investigate the system.

Fig 7. Encoding and deciphering circuit of an (8, 4) even Latin square code Linear Feedback Shift Register Plan in VHDL

# LFSR represents the direct criticism shift register. Even though they are broadly utilized in irregular

hardware projects they are regularly ignored by the architect's local area. this is included a progression of D-goes back and forth, contingent upon the size of the LFSR. A portion of the states and particularly the last one is input to the framework by going through coherent XOR.

# The purpose

The principal utilization of LFSR is to create rationale/arbitrary numbers. Notwithstanding, the large benefit is next state can be known whether the sources of info are known. This control means the world to equipment engineers. They used to create test designs for a given circuit by knowing the states for LFSR. They are shaped to go about as a counter or occasion generator by LFSR. LFSR can be united to shape a flowed circle at its finishes. So, a shift register whose info bit is a direct capacity of its past state is a straight input shift register (LFSR). This is a pivoting register, in which one of the Flip-Flops has a XOR as its feedback, a XOR among at least two results of the leftover Flip-Flops. The results are associated with the XOR Gate.

## **Error Correction with LFSRs**

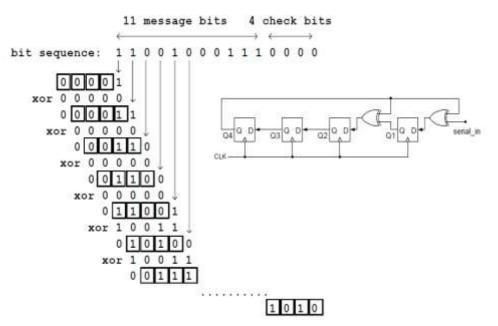

Fig 8. Error Correcting with LFSR

# UGC Care Group I Journal Vol-12 Issue-08 No. 07 August 2022

Approaching piece successions XOR Q4. Presently upsides of shift-register don't follow a decent example in the information grouping. The worth of the register after 15 cycles is taken a gander at as "1010". The number of various nonzero designs for the first LFSR has noticed the length of the info succession is 24-1 = 15 same as. The paired message possesses just 11 pieces, the leftover 4 pieces are "0000". The end-product is supplanted by our LFSR would be: "1010". If the grouping concerning the LFSR with the supplanted bits, we would get "0000" the eventual outcome then we run the arrangement back through 4 equality bits, "kill".

On the off chance that equality pieces are not every one of the zero, a blunder happened in transmission. In the event that various equality bits  $= \log a$  complete number of pieces, then single piece mistakes can be rectified. greater equality bits permit utilizing more blunders to be recognized. 32 equality bits for every casing/bundle utilized Ethernet with 16-bit LFSR.

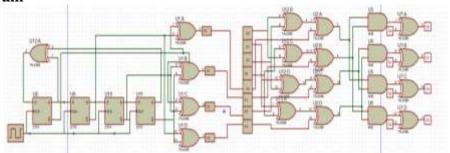

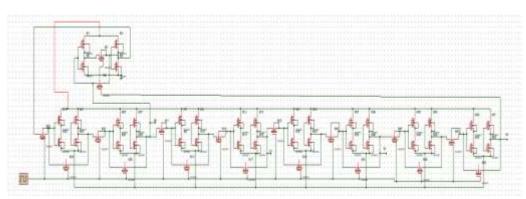

## EDA TOOL IMPLEMENTATION Logical Diagaram

Fig 9.Logical Diagaram Hamming Code with Lfsr

Fig 10. Lfsr with EDA Tool

Fig 11.Hamming Code with EDA Tool

Hamming Code

**LFSR**

# Dogo Rangsang Research Journal ISSN : 2347-7180 Hamming Code using LFSR

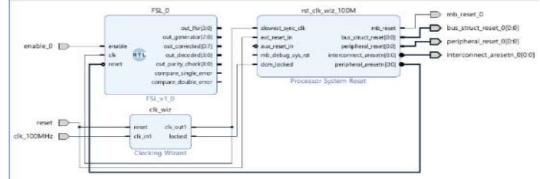

# Vivado Tool Implementation Block Diagram

Fig 14. Block Diagram Generated in Vivado Tool

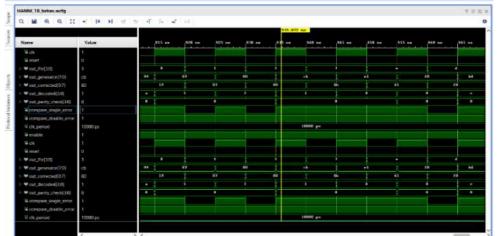

# **Simulated Output**

Fig 15. Simulated Output Generated in Vivado Tool

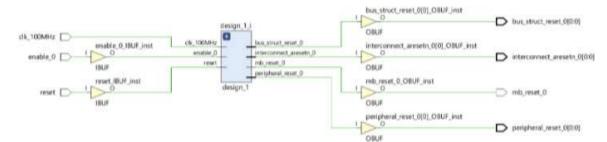

## **RTL View**

Fig 16. RTL VIEW in Vivado Tool

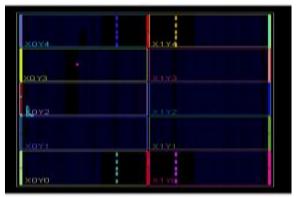

## **Implementation View**

Fig 17. Implementation View in Vivado tool:

Fig 18. Code Dumping in Zynq Evaluation Board

## CONCLUSION

Blunder recognition and adjustment abilities have been recreated and carried out by the Design of Hamming encoder and decoder. The framework has been planned utilizing SoC The plan incorporates both the encoder-decoder frameworks to be utilized for the sequential information transmission and gathering of the remote handset frameworks. The plan has been reenacted and Vivado2019.1 is utilized to check the VHDL and Simulator. Xilinx zynq-7000 SoC zc702 assessment unit for Xilinx 19.1 has been utilized for the Simulation and Synthesis. The proposed plan and recreation tests are completed utilizing the EDA Tool. There are various measurements are used for estimating the presentation of Hamming codes. The recreation explores results demonstrate the prevalence of the proposed information encoding instrument contrasted with the conventional methodology. The proposed approach for Hamming codes execution accomplishes 50 % H/W straightforwardness for the Hamming codes (8, 4) contrasted with the CMOS approach. This approach can be reasonable for carrying out complex blunder control plans.

## REFERENCES

- X. Guan, D. Zhou, D. Wang, Y. Yang and Z. Zhu, "A Case Study on Fully Asynchronous ACS Module of Low-power Viterbi Decoder for Digital Wireless Communication Applications," 2009 International Conference on Computational Intelligence and Natural Computing, 2009, pp. 426-429, doi: 10.1109/CINC.2009.64.

- M. Kawokgy and C. A. T. Salama, "Low-power asynchronous Viterbi decoder for wireless applications," Proceedings of the 2004 International Symposium on Low Power Electronics and Design (IEEE Cat. No.04TH8758), 2004, pp. 286-289, doi: 10.1145/1013235.1013306.

- 3. S. Ranpara and Dong Sam Ha, "A low-power Viterbi decoder design for wireless communications applications," Twelfth Annual IEEE International ASIC/SOC Conference (Cat. No.99TH8454), 1999, pp. 377-381, doi: 10.1109/ASIC.1999.806538.

- 4. C. Chen, C. Yu, M. Yen, P. Hsiung and S. Chen, "Design of a low power viterbi decoder for wireless communication applications," IEEE International Symposium on Consumer Electronics (ISCE 2010), 2010, pp. 1-4, doi: 10.1109/ISCE.2010.5523702.

- S. R. Surya, K. Balasubramanian and B. Yamuna, "Design of a low power and high-speed Viterbi decoder using T-algorithm with normalization," 2021 International Conference on Advances in Computing and Communications (ICACC), 2021, pp. 1-6, doi: 10.1109/ICACC-202152719.2021.9708202.

- 6. W. -L. Su, H. Chiueh, P. -T. Huang and W. Hwnag, "A Low Power Pulsed Edge-Triggered Latch for Survivor Memory Unit of Viterbi Decoder," 2006 13th IEEE International Conference on Electronics, Circuits and Systems, 2006, pp. 553-556, doi: 10.1109/ICECS.2006.379848.

- 7. H. Suzuki, Yun-Nan Chang and K. K. Parhi, "Low-power bit-serial Viterbi decoder for 3rd

#### UGC Care Group I Journal Vol-12 Issue-08 No. 07 August 2022

generation W-CDMA systems," Proceedings of the IEEE 1999 Custom Integrated Circuits Conference (Cat. No.99CH36327), 1999, pp. 589-592, doi: 10.1109/CICC.1999.777350.

- 8. J. Jin and C. Tsui, "A Low Power Viterbi Decoder Implementation using Scarce State Transition and Path Pruning Scheme for High Throughput Wireless Applications," ISLPED'06 Proceedings of the 2006 International Symposium on Low Power Electronics and Design, 2006, pp. 406-411, doi: 10.1145/1165573.1165673.

- 9. Wing-Kin Chan, Chiu-Sing Choy, Cheong-Fat Chan and Kong-Pang Pun, "An asynchronous SOVA decoder for wireless communication application," 2004 IEEE International Symposium on Circuits and Systems (ISCAS), 2004, pp. II-517, doi: 10.1109/ISCAS.2004.1329322.

- 10. H. Suzuki, Yun-Nan Chang and K. K. Parhi, "Low-power bit-serial Viterbi decoder for next generation wide-band CDMA systems," 1999 IEEE International Conference on Acoustics, Speech, and Signal Processing. Proceedings. ICASSP99 (Cat. No.99CH36258), 1999, pp. 1913-1916 vol.4, doi: 10.1109/ICASSP.1999.758298.

- <sup>11.</sup> Leena, Mr. Subham Gandhi and Mr. Jitender Khurana, "Implementing(7,4) Hamming Code using CPLD on VHDL" International Journal of New Trends in Electronics , Vol. 1, Issue 1, Aug. 2013.

- 12. Xilinx "ZYNQ7000 SoC Family, complete datasheet", Xilinx Corp., Aug 2005.

- 13. Xilinx "Synthesis and Simulation Design Guide", Xilinx Tech ug925-zynq-zc702-base-trd.

- 14. Ming- Bo Lin "Digital System Design and Practices using Verilog HDL and FPGA", Wiley-India , ISBN:978-81-265-3694-8.

- 15. Shu Lin, Daniel J. Costello. J "Error Control coding; Fundaments & applications", Prentice Hall , ISBN 0-13-283796-X.1983.

- 16. Yan, J.; Zhang, W. Evaluating Instruction Cache Vulnerability to Transient Errors. In Proceedings of the ACM Workshop on Memory Performance: Dealing with Applications, Systems and Architectures (MEDEA), Seattle, WA, USA, 1–2 September 2006; pp. 21–28. [CrossRef]

- 17. Tang, L.; Mars, J.; Vachharajani, N.; Hundt, R.; Soffa, M.L. The Impact of Memory Subsystem Resource Sharing on Datacenter Applications. In Proceedings of the 38th International Symposium on Computer Architecture (ISCA), San Jose, CA, USA, 4–8 June 2011; pp. 283–294. [CrossRef]

- 18. Baumann, R.C. Radiation-Induced Soft Errors in Advanced Semiconductor Technologies. IEEE Trans. Device Mater. Reliab. **2005**, *5*, 305–316. [CrossRef].

- 19. Nuh Aydin: An Introduction to Coding Theory via Hamming Codes. Department of Mathematics Kenyon College.

- 20. Ranpara, S.; Dong Sam Ha, 1999. A low-power Viterbi decoder design for wireless communications applications. IEEE Proceedings of the Twelfth Annual IEEE International Int. ASIC Conference 1999, Washington, DC, 15-18 Sept. 1999, pp. 377-381.

21. Xilinx "Spartan-3 FPGA Family, complete